抖音代理ip显示未知

技术即将来到奇点的时候,美国出手将浪潮、 龙芯列入实体清单。这明显是在压制中国人工智能产业。

Chiplet是一种全新的芯片设计理念为了便于理解,咱们先来看看目前的芯片是怎么设计出来的。

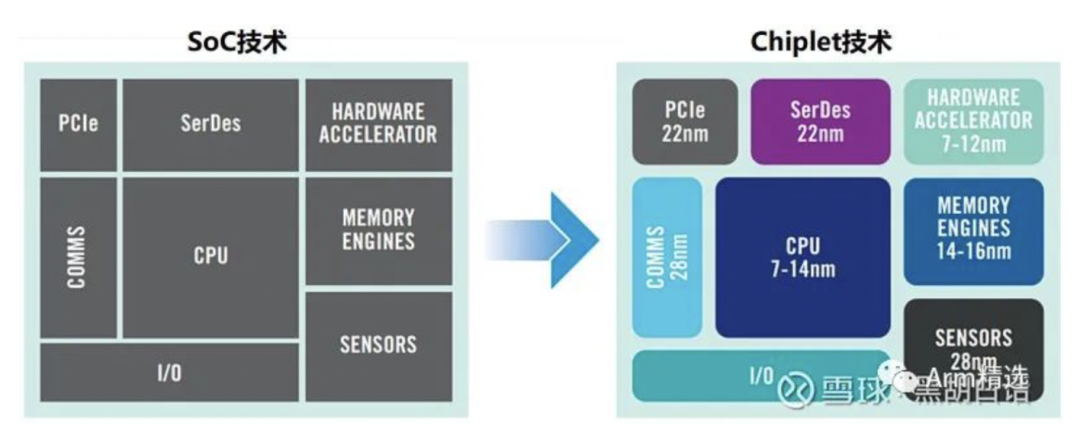

大家会经常听到SoC这样一个芯片代名词。它是把很多的功能模块,比如CPU、存储器、接口这些通通集成在一个芯片上,做成一个大芯片。

在Chiplet设计理念下,是将原本SoC中的每个功能模块都单独拆出来,做成具有单独功能的一个个小芯片单元。

SoC(system on chip)叫做片上系统。是围绕CPU,将各种功能模块都集成在一颗芯片上的产物。

在SoC中,由于是在一个芯片中进行集成的,所以各个功能模块必须采用同一工艺制程,要是14nm的都是14nm的,要是7nm的都得是7nm的。

而在Chiplet模式下,不同工艺的芯片可以凑到一起。比如CPU用7nm的,接口芯片用14nm的。这就是异构的概念。

异质集成,是指不同材料的芯片可以集成为一体。SoC肯定是办不到的。而Chiplet模式下,可以将Si、GaN、InP等等不同材质的小芯片集成到一起。

SiP(system in package)指系统级封装。通过将多种功能的芯片,包括处理器、存储器、FPGA等功能芯片集成在一个封装内,从而实现一个完整的系统。

在概念上来讲,SiP与Chiplet很像。并且SiP同样能够实现异构异质集成的。而它们两者的区别在于,SiP是将不同芯片封装在一个基板上,Chiplet则是封装到芯片上。

因此,Chiplet还是属于芯片,而SiP只能算作小系统。Chiplet能达到SoC的性能 而SiP则不一样,因此Chiplet多用于高性能领域,SiP多用于小型化消费级产品。

了解了Chiplet的概念,可能有人会说,相比SoC,Chiplet工序既繁琐、又无法完全超越SoC的性能,这不是脱裤子放屁多此一举嘛。

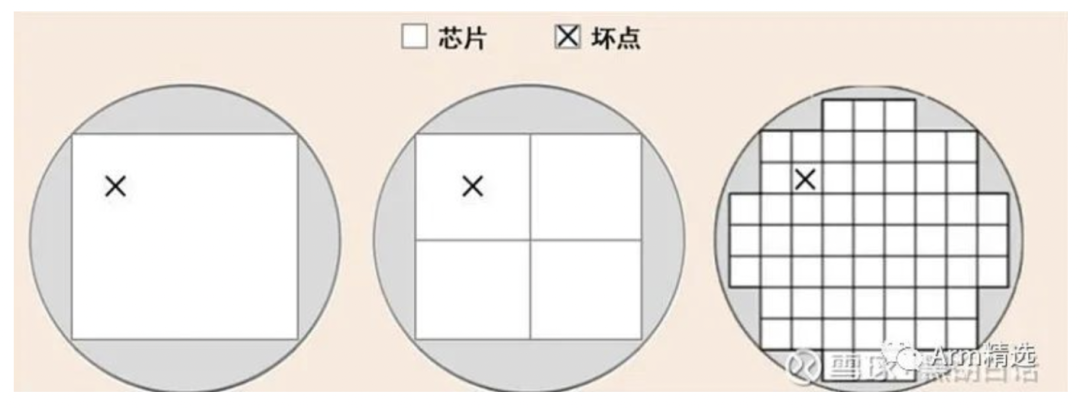

1. 提升良率: 在芯片制造过程中,一片晶圆有固定的缺陷率。遇到这些无法修复的坏点,只能把它剔除掉。

当一颗芯片的尺寸达到400甚至600平方毫米时,芯片的良率就会变的很低。这个时候,采用Chiplet模式,将大芯片拆成一个个小芯片的制造成本就会有优势。

在系统级芯片上,很多功能模块都是标准化的。那么在Chiplet模式下,应商就可以生产出很多标准化的芯粒,下游客户直接购买芯粒进行封装就可以了。

此外,Chiplet模式具有异构集成的特点。有时候一颗高性能芯片,只需要CPU满足更高制程,其他芯片制程低一些没关系。

比如AMD在第三代锐龙(Ryzen)处理器上就沿用了第二代霄龙(EPYC)处理器的I/O芯片。

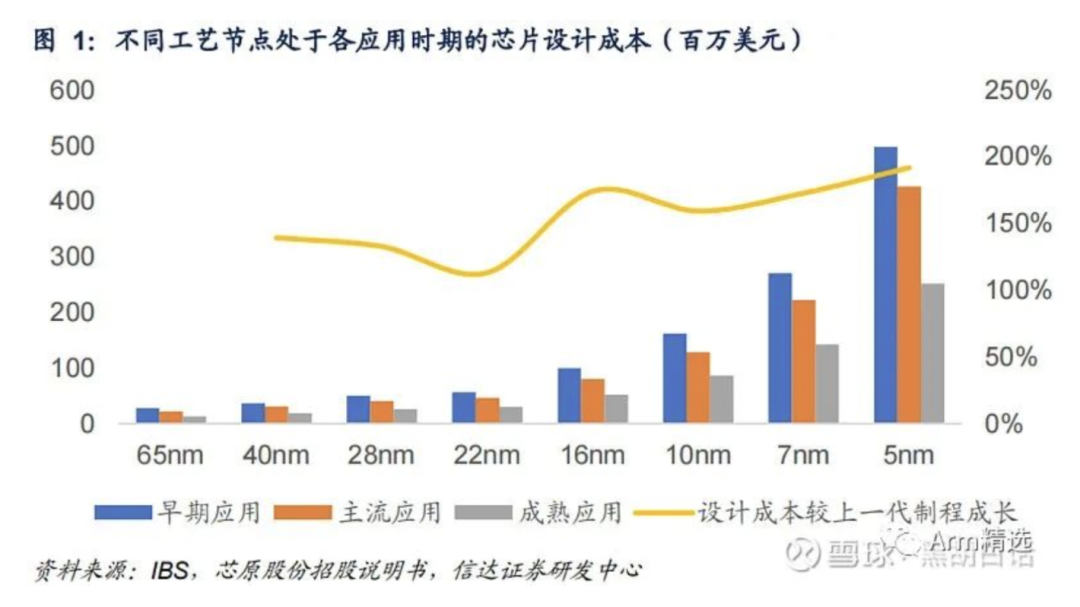

在工艺节点为 28nm 时,单颗芯片设计成本约为 0.41 亿美元,而工艺节点为 7nm 时,设计成本快速提升至 2.22 亿美元。

目前Chiplet具有两个设计思路。一个是按照功能将不同模块拆分,比如AMD的三代锐龙处理器。

比如苹果的M1 Ultra芯片,就是堆叠了两颗M1 Max芯片,从而获得两倍算力。 那么在第二种思路下,理论上可以通过Chiplet的堆叠,让低端产品实现高端产品的性能。

目前美国对中国高端制程芯片的封锁很严密,那我们就采用Chiplet技术,拿14nm、28nm的芯片堆出7nm、5nm的效果。所以这也是Chiplet概念近期炒作的逻辑之一。

Chiplet只能说是一种芯片的设计理念,真的要把一个个芯粒拼装在一起,关键得看封装技术能不能跟得上。

不同芯粒之间如何实现互联互通,需要在下层PCB板与上层芯粒间,加入一片硅中介板(Silicon Interposer)。

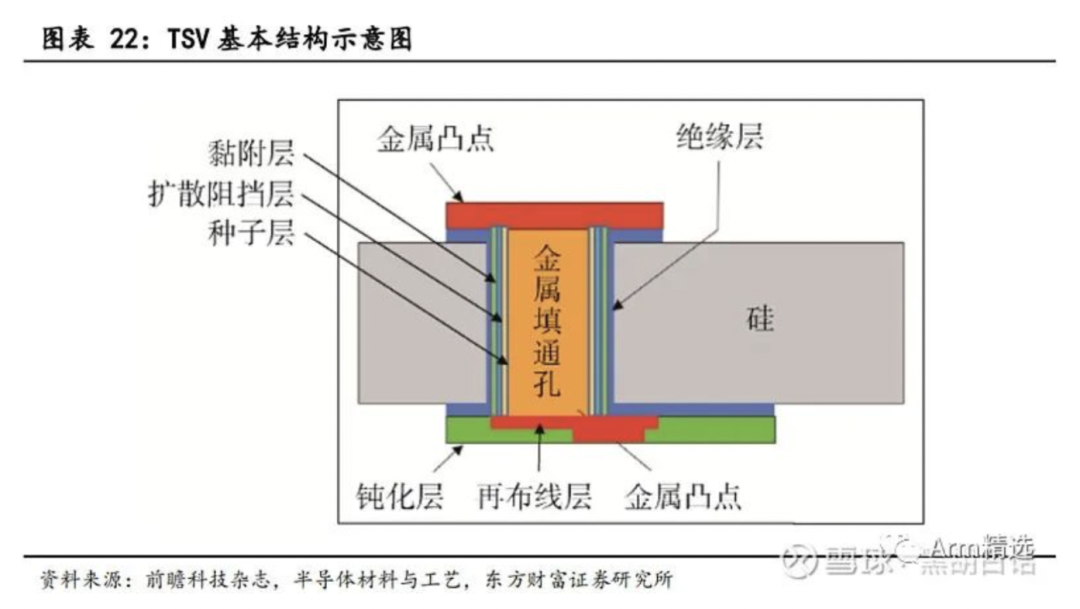

硅中介板本身没什么特别的,类似于一颗没有功能的晶圆。但难点在于,要在Interposer内部做很多硅通孔(TSV),起到电气垂直互联的作用。

这个工艺难度还是不小的。目前2.5D封装代表技术有三种,分别是台积电的CoWoS、英特尔的EMIB以及三星的I-Cube。

3D封装相比2.5D能够实现更高密度的堆叠。相比2.5D,小芯片可以直接摞在一起,这就需要在小芯片内直接制作硅通孔(TSV)。因此难度更大。

目前3D封装技术还不是很成熟。比较完善的是应用在DRAM领域,可以实现100多层的上下堆叠,但这都是同质范畴的,异质堆叠还没那么快。

3D封装技术目前主要有台积电的SoIC、英特尔的Foveros、三星的X-Cube。看到没,还是这三家公司。它们的共同特点是都有晶圆制造能力,利用卡位优势,开发自己的先进封装技术。

当然传统封测厂同样也没闲着,在2.5D/3D封装技术上都有布局。比如国内通富微电、长电科技等等。

这波AIGC的风口为什么能把Chiplet概念带起来?他们之间有两个维度的关系。 第一点在前面文章中提到过,在美国技术封锁的背景下,咱们有望通过Chiplet架构去堆叠芯片的性能,支持算力基础。属于解决开脖子的逻辑。

而第二点呢,目前Chiplet模式下产出的芯片,只有在高性能领域才有切实的需求。这与人工智能需要的大算力芯片不谋而合。

前面也讲到过,Chiplet概念的诞生,其实是为了解决SoC芯片越来越大、制程越来越高以后产生的弊端。比如良率下降、设计成本增加、研发周期更长等问题。

比如就拿芯片尺寸来说,200、300平方毫米以下的芯片,根本就不用做成Chiplet架构,SoC芯片是最优解。

但当芯片尺寸来到600、800平方毫米甚至更高的时候,也许一颗SoC芯片的性能是提高了1倍、2倍,但所投入的综合成本将是5倍、10倍的增长。这个时候Chiplet模式的经济效益就凸显出来了。

也就是说AIGC如果迎来爆发式增长,那么对于算力的需求会持续扩张,AI芯片再迭代下去,Chiplet模式将成为主流。最终带动Chiplet产业链实现快速增长。

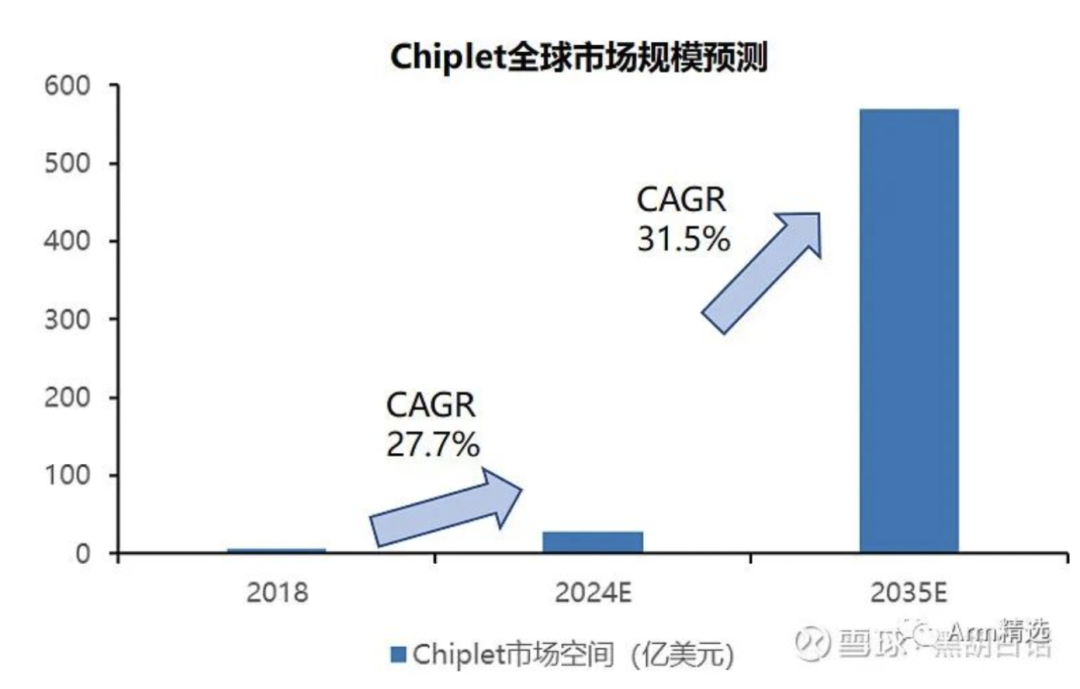

根据Omdia的预测,到2024年,Chiplet的全球市场空间会达到58亿美元,到2035年,市场空间将增长到570亿美元,年均增速超过30%。

大家不要觉得很夸张,根据WSTS数据,2022年全球半导体市场规模为5735亿美元。570亿美元只是今天全市场的十分之一。

在半导体发展早期,没有IP核这个概念,每设计一款芯片,电路都要重新设计。之后大家发现,其实芯片中有很多功能都是相似的,那能不能把这些部分变成模块化,以后再设计芯片时,直接拿过来用就可以了。这就是IP核存在的逻辑。

现在要设计一款SoC芯片,设计企业会从IP供应商那里先购买一些IP核,再结合自研模块,集成为一个SoC。

IP核就成为了芯片设计环节中的复用产品。好比你要设计一款汽车,轮毂的式样直接用别人的就可以了。

而在Chiplet下,这种产业链模式会发生变化。核心在于传统的IP核只停留在设计层面,可Chiplet中,IP核可以直接变成一颗颗芯粒,这就形成了硅片形态。

还是拿汽车举例,Chiplet模式下,IP核不再是设计层面的轮毂式样,而是变成了实实在在制造好的汽车轮毂。

这样一来,首先,IP供应商的收入结构变了,以前是IP授权,现在是芯片销售。由于捆绑了芯片制造环节,收入规模会增加。

其次,IP供应商的下游客户将从芯片设计企业转变为芯片直接需求方。比如互联网公司、手机电脑制造商这些。那相当于IP供应商从tier2变成了tier1,等级进阶了。

其一,之前提到,Chiplet需要先进封装技术的支撑。先进封装工艺难度大,价值量自然更高,这有益于提升封测厂的盈利水平。

其二,Chiplet模式下,伴随着产业链结构的变化。未来很有可能,下游产品公司购买小芯片,之后直接找OSAT企业去集成芯片。对于OSAT厂相当于拓展了优质客户,同时提升了产业链的地位。

其三,把一颗大的SoC拆成几个小的Chiplet,之前可能只测一个关键参数,现在每个小芯片都要做测试。相当于增加了封测厂的测试需求。

当然,外包封测厂未来面临着晶圆代工厂的竞争,毕竟人家掌握着核心制造环节,再提供封装服务,是顺理成章的。

EDA: EDA是芯片设计的辅助软件。随着芯片线宽不断缩小,EDA的作用越来越突显。 而传统EDA的思路与Chiplet模式是有些矛盾的,缺乏对于芯片与封装之间影响的考虑。导致芯片在2.5D、3D堆叠封装后效率上不去。

所以针对Chiplet,EDA也应该考虑新的架构。这一变化对于国内EDA企业去追赶海外龙头是有所帮助的。就好比国内车企在内燃机时代玩不过海外巨头,但电动车咱们是一个起跑线。

当然这个比喻太夸张了,国内EDA企业还有很多短板要补上,不可能说一个Chiplet时代就实现逆袭。

说了那么多关于Chiplet的好,我们也要去分析分析它的难点与短板在哪里。 首先要说的是关于性能这个话题,通过Chiplet方式堆叠芯片,是可以提高性能,但目前效率不高。

按照华为之前测试的结果,拿2个14nm芯片做堆叠,只能达到10nm芯片的性能。用5个14nm的芯片,才能接近7nm水平。

这里面的问题与封装工艺有关,与EDA软件有关,总之传输速率、散热、干扰这些问题没法完美解决。

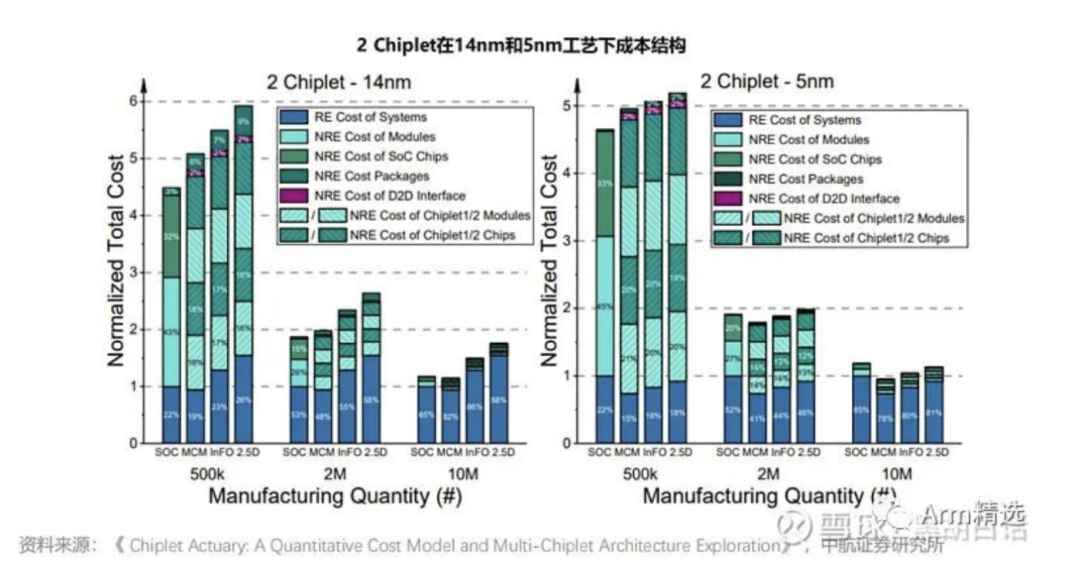

其次是效益问题。Chiplet要用到先进封装,虽然目前2.5D封装技术已经商业化了,但封装成本还是很高的。

在14nm上,2.5D封装比SoC成本还是高的,没有效益优势。只有到5nm水平,规模化后,2.5D封装才比SoC有更低的成本。

所以按照目前的状态,Chiplet只能替代高制程、大尺寸的SoC芯片。应用空间还是比较狭小的。

还有就是接口标准的问题。目前Chiplet的发展比较初级,基本是自己搞自己的。而要想达到设想的终极状态,芯粒能像IP核一样在市场流通,所有芯片的互联标准必须要统一起来。

目前英特尔建立了小芯片联盟(UCIe),中国也开始制定小芯片接口技术标准。但中美关系或许是个羁绊,制约整个Chiplet产业的发展。

最后,还是要说说“卡脖子”这件事抖音代理ip显示未知。如果漂亮国对咱们的技术封锁只是小打小闹,通过Chiplet或许我们在大算力芯片上不至于输的太惨。

而如果是全面打击、晶圆制造、设备、材料、甚至EDA软件每个环节都设置障碍,Chiplet根本没法解决“卡脖子”问题。

前面文章提到,Chiplet模式下,对于IP核企业,以及封测企业,尤其是具有先进封装技术的封测企业整体上是利好的。

先说IP核企业。目前A股比较纯的公司有一家,叫芯原股份。它的业务收入可以总结为两大块。一个是帮下游产品客户定制芯片,既可以设计、也可以找代工厂生产。另一块业务就是IP授权。

总的来说,从业务纯度、产品线贴合度、以及市场的稀缺程度来看,芯原股份是比较受益Chiplet概念的标的。

下面再来说说封测企业。由于传统封测技术壁垒不高,中国已经承接了来自全球的封测业务。在全球排名靠前的企业包括长电、通富、华天这些。

由于这些龙头企业的技术实力靠前,在先进封装技术上都或多或少有建树,因此都算Chiplet利好标的。

通富微电2016年收购了AMD的封测业务,从此就傍上了“大佬”,与AMD深度捆绑,承接了AMD大部分封测订单。

而AMD算是Chiplet方案的开山鼻祖,2019年的锐龙2处理器,就使用了Chiplet架构。也是因为Chiplet技术的加持,AMD把英特尔干的不行。

目前公司已建成国内顶级超大尺寸FCBGA研发平台与2.5D/3D封装平台(VISionS)。并且已经开始大规模生产Chiplet 产品了。

最后总结一下。Chiplet在需求端确实会受益AIGC的发展在供给端则要看先进封装技术的不断突破。

有人可能会问,为什么GPU大佬英伟达还没有使用Chiplet?可能因为它的产品附加值太高了,现在过的还很舒服。但当英伟达准备上chiplet的时候,chiplet的大势或许就真的来了。

文章出处:【微信号:Ithingedu,微信公众号:安芯教育科技】欢迎添加关注!文章转载请注明出处。

也是长电科技重点发展的技术。“目前我们重点发展几种类型的先进封装技术。首先就是系统级封装(

芯片,从设计时就先按照不同的计算单元或功能单元对其进行分解,然后每个单元选择最适合的半导体制程工艺进行分别制造,再通过先进封装技术将各个单元彼此互联,最终集成封装为一个系统级芯

将满足特定功能的裸芯片通过Die-to-Die内部互联技术,实现多个模块芯片与底层基础芯片的系统封装,实现一种新形势的IP复用。

关键技术与挑战 /

? 在当今的半导体技术领域,尺寸越来越小,性能越来越高的芯片成为了主流。然而,随着芯片数量和面积的不断增加,传统的单一芯片设计面临了越来越多的挑战。为了应对这些挑战

? 随着技术的不断发展,芯片设计也在快速演变。而在芯片设计理念中,目前最常见的概念是system-on-a-chip (

和CoWoS是现代半导体工业中的两种关键概念。两者都具有很高的技术含量和经济意义。本文将详细介绍